SuperH, often abbreviated as SH, is a RISC ISA developed by Hitachi. SuperH went through several iterations, starting from SH-1 and moving up to SH-4. The more recent SH-5 has two modes of operation, one of which is identical to the user-mode instructions of SH-4, while another, SHmedia, is quite different. Each family takes its own market niche:

- SH-1: Home appliances

- SH-2: Car controllers and video game consoles such as Sega Saturn

- SH-3: Mobile applications such as car navigators

- SH-4: Car multimedia terminals and video game consoles such as Sega Dreamcast

- SH-5: High-end multimedia applications

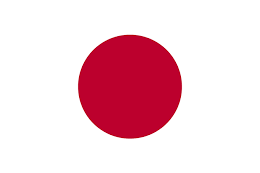

Microcontrollers and CPUs implementing it are currently produced by Renesas Electronics, a joint venture of the Hitachi and Mitsubishi Semiconductor groups. As IoT malware mainly targets SH-4-based systems, we will focus on this SuperH family.