I2C bus

The third serial communication protocol analyzed in this chapter is I2C. From the communication strategy point of view, this protocol shares some similarities with SPI. However, the default bit rate for I2C communication is much lower, as the protocol privileges lower-power consumption over throughput.

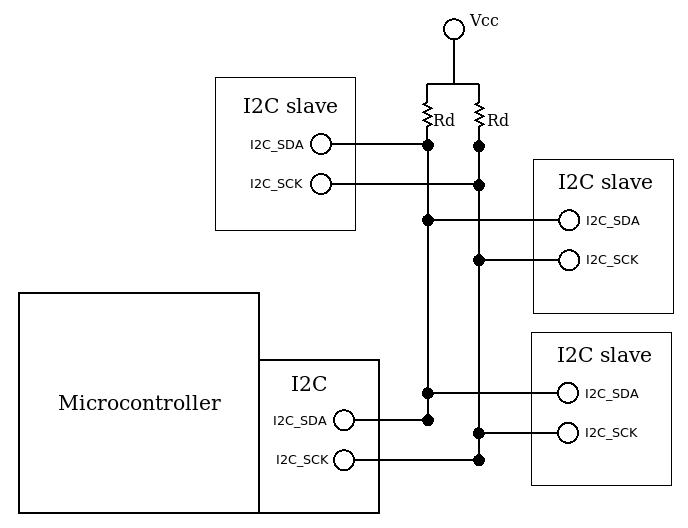

The same two-wire bus can accommodate multiple participants, both master and slaves, and there is no need for extra signals to physically select the slave of the transaction, as slaves have fixed logic addresses assigned:

I2C bus with three slaves and external pull-up resistors

One wire transports the clock generated by the master, and the other is used as a full-duplex, bidirectional synchronous data path. This is possible thanks to the unique mechanism of arbitration of the channel, which relies on the electronic design of the transceivers, and may deal with the presence of multiple masters on the same bus in a very clean way.

The two signals must be connected to the high-level voltage...